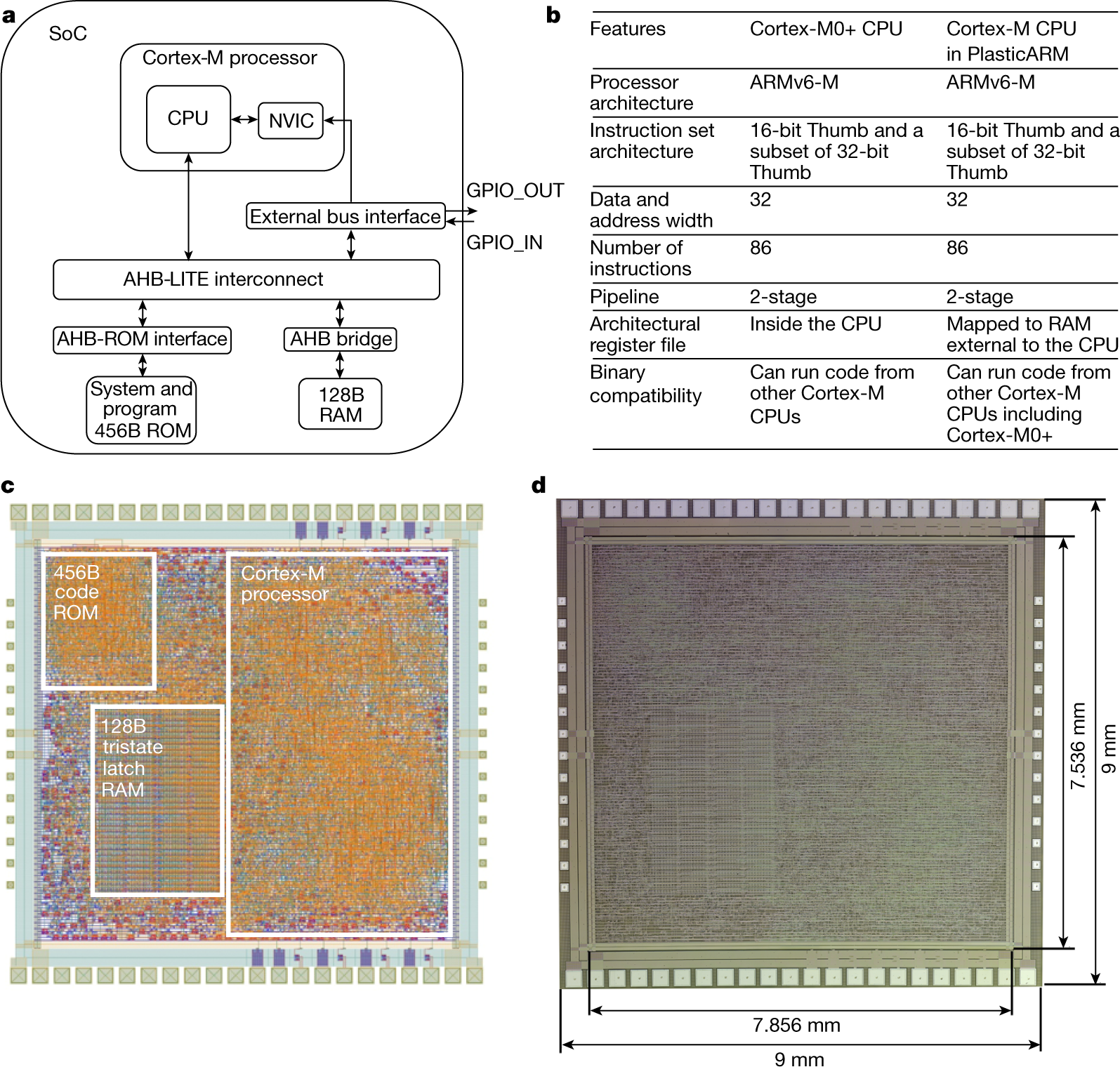

Fig. 1: PlasticARM architecture and features.

a, The SoC architecture, showing the internal structure, the processor and system peripherals. The processor contains a 32-bit Arm Cortex-M CPU and a Nested Vector Interrupt Controller (NVIC), and is connected to its memory through the interconnect fabric (AHB-LITE). Finally, the external bus interface provides a General-Purpose Input-Output (GPIO) interface to communicate off-chip with the test framework. b, Features of the CPU used in PlasticARM compared to those of the Arm Cortex-M0+ CPU. Both CPUs fully support Armv6-M architecture with 32-bit address and data capabilities and a total of 86 instructions from the entire 16-bit Thumb and a subset of 32-bit Thumb instruction set architecture. The CPU microarchitecture has a two-stage pipeline. The registers are in the CPU of the Cortex-M0+, but in the PlasticARM the registers are moved to the latch-based RAM in the SoC to save the CPU area of the Cortex-M. Finally, both CPUs are binary compatible with each other and to other CPUs in the same architecture family. c, The die layout of PlasticARM, denoting the key blocks in white boxes such as the Cortex-M processor, ROM and RAM. d, The die micrograph of PlasticARM, showing the dimensions of the die and core areas.